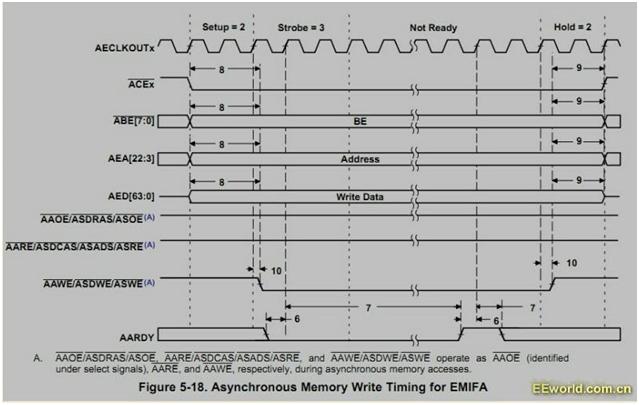

DSP与FPGA采用EMIF接口通信,即将FPGA作为DSP的外部SRAM,只需设置EMIF控制的存储器为SRAM类型即可,DSP通过EMIF接口读写SRAM的时序如下: 参考datasheet《tms320dm642.pdf》

可以根据以上时序图编写FPGA代码,以下仅供参考:moduleDSP_FPGA(

input clk,

input [2:0] addr, //简单测试,没有用到所有地址

inout[15:0] data, //16位数据宽度

input CE_2,//FPGA片选

input AOE,

input AWE

);

reg [15:0]DSP_FPGA_REG0;

reg [15:0]DSP_FPGA_REG1;

reg [15:0]DSP_FPGA_REG2;

reg [15:0]DSP_FPGA_REG3;

reg [15:0]DSP_FPGA_REG4;

reg [15:0] DSP_FPGA_REG5;

reg [15:0]DSP_FPGA_REG6;

reg [15:0]DSP_FPGA_REG7;

wire rd_en = ~CE_2 && ~AOE;reg [15:0] data_reg;

//always @(posedge clk) //DSP读操作,The samplingpoint of DSP reading is the risging edge ofAWE!

always @(*) //这里没有用时钟,用的latch

begin

if(rd_en)

begin

case(addr[2:0])

3'd0 : data_reg <= DSP_FPGA_REG0;

3'd1 : data_reg <= DSP_FPGA_REG1;

3'd2 : data_reg <= DSP_FPGA_REG2;

3'd3 : data_reg <= DSP_FPGA_REG3;

3'd4 : data_reg <= DSP_FPGA_REG4;

3'd5 : data_reg <= DSP_FPGA_REG5;

3'd6 : data_reg <= DSP_FPGA_REG6;

3'd7 : data_reg <= DSP_FPGA_REG7;

default: ;

endcase

end

end

reg AWE_tmp1;

reg AWE_tmp2;

always @(posedge clk)

begin

AWE_tmp1 <= AWE;

AWE_tmp2 <= AWE_tmp1;

end

wire AWE_RISING = ~AWE_tmp2 && AWE_tmp1;//与clk同步

always@(*)

begin

if(AWE_RISING) //这里也没有用时钟,用的是latch

begin

case(addr[2:0])

3'd0 : DSP_FPGA_REG0 <= data;

3'd1 : DSP_FPGA_REG1 <= data;

3'd2 : DSP_FPGA_REG2 <= data;

3'd3 : DSP_FPGA_REG3 <= data;

3'd4 : DSP_FPGA_REG4 <= data;

3'd5 : DSP_FPGA_REG5 <= data;

3'd6 : DSP_FPGA_REG6 <= data;

3'd7 : DSP_FPGA_REG7 <= data;

default: ;

endcase

end

end assign data = rd_en ? data_reg : 16'hzzzz;

endmodule

//////////////////////////////////////////////////////////

DSP(具体为DM642)端程序:寄存器设置参考 《EMIF ReferenceGuide- spru266b.pdf》 即spru266

#define FPGA_ADDR 0xA0000000

//#define EMIFA_GBLCTL 0x01800000

#define EMIFA_CECTL2 0x01800010 //#define EMIFA_CESEC2 0x01800050

void delay(unsigned long time)

{

unsigned long i;

for(i = 0; i < 1000; i++)

{

for(; time >0 ; time--)

{

}

}

}

unsigned short write_value = 0;

unsigned short read_value = 0;

int main(void)

{

unsigned short *ptr;

*(unsigned volatile int *)EMIFA_CECTL2 =(unsigned int)0xFFFFFF13;//设置EMIF控制的存储器类型为 //16位宽SRAM ptr = (unsigned short*)(unsigned int)FPGA_ADDR;

while(1)

{

*ptr = write_value;

read_value= *ptr; //调试时通过观察write_value与read_value的值是否相等可以检验通信是否正常

delay(100000);

write_value++;

}

return 0;

} 实际测试发现写入与读出的值相同

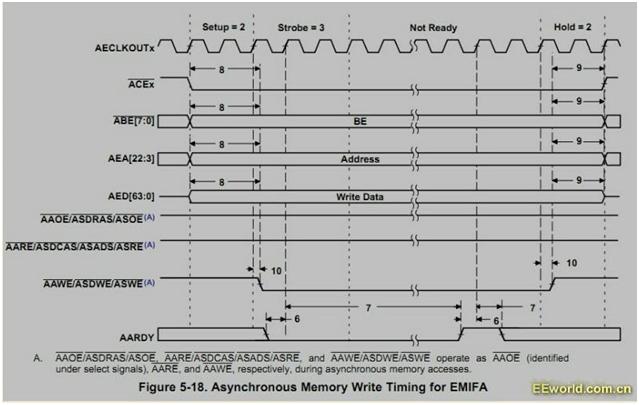

可以根据以上时序图编写FPGA代码,以下仅供参考:moduleDSP_FPGA(

input clk,

input [2:0] addr, //简单测试,没有用到所有地址

inout[15:0] data, //16位数据宽度

input CE_2,//FPGA片选

input AOE,

input AWE

);

reg [15:0]DSP_FPGA_REG0;

reg [15:0]DSP_FPGA_REG1;

reg [15:0]DSP_FPGA_REG2;

reg [15:0]DSP_FPGA_REG3;

reg [15:0]DSP_FPGA_REG4;

reg [15:0] DSP_FPGA_REG5;

reg [15:0]DSP_FPGA_REG6;

reg [15:0]DSP_FPGA_REG7;

wire rd_en = ~CE_2 && ~AOE;reg [15:0] data_reg;

//always @(posedge clk) //DSP读操作,The samplingpoint of DSP reading is the risging edge ofAWE!

always @(*) //这里没有用时钟,用的latch

begin

if(rd_en)

begin

case(addr[2:0])

3'd0 : data_reg <= DSP_FPGA_REG0;

3'd1 : data_reg <= DSP_FPGA_REG1;

3'd2 : data_reg <= DSP_FPGA_REG2;

3'd3 : data_reg <= DSP_FPGA_REG3;

3'd4 : data_reg <= DSP_FPGA_REG4;

3'd5 : data_reg <= DSP_FPGA_REG5;

3'd6 : data_reg <= DSP_FPGA_REG6;

3'd7 : data_reg <= DSP_FPGA_REG7;

default: ;

endcase

end

end

reg AWE_tmp1;

reg AWE_tmp2;

always @(posedge clk)

begin

AWE_tmp1 <= AWE;

AWE_tmp2 <= AWE_tmp1;

end

wire AWE_RISING = ~AWE_tmp2 && AWE_tmp1;//与clk同步

always@(*)

begin

if(AWE_RISING) //这里也没有用时钟,用的是latch

begin

case(addr[2:0])

3'd0 : DSP_FPGA_REG0 <= data;

3'd1 : DSP_FPGA_REG1 <= data;

3'd2 : DSP_FPGA_REG2 <= data;

3'd3 : DSP_FPGA_REG3 <= data;

3'd4 : DSP_FPGA_REG4 <= data;

3'd5 : DSP_FPGA_REG5 <= data;

3'd6 : DSP_FPGA_REG6 <= data;

3'd7 : DSP_FPGA_REG7 <= data;

default: ;

endcase

end

end assign data = rd_en ? data_reg : 16'hzzzz;

endmodule

//////////////////////////////////////////////////////////

DSP(具体为DM642)端程序:寄存器设置参考 《EMIF ReferenceGuide- spru266b.pdf》 即spru266

#define FPGA_ADDR 0xA0000000

//#define EMIFA_GBLCTL 0x01800000

#define EMIFA_CECTL2 0x01800010 //#define EMIFA_CESEC2 0x01800050

void delay(unsigned long time)

{

unsigned long i;

for(i = 0; i < 1000; i++)

{

for(; time >0 ; time--)

{

}

}

}

unsigned short write_value = 0;

unsigned short read_value = 0;

int main(void)

{

unsigned short *ptr;

*(unsigned volatile int *)EMIFA_CECTL2 =(unsigned int)0xFFFFFF13;//设置EMIF控制的存储器类型为 //16位宽SRAM ptr = (unsigned short*)(unsigned int)FPGA_ADDR;

while(1)

{

*ptr = write_value;

read_value= *ptr; //调试时通过观察write_value与read_value的值是否相等可以检验通信是否正常

delay(100000);

write_value++;

}

return 0;

} 实际测试发现写入与读出的值相同