Cortex M0+内核芯片开关外设中断

1、引言

本文将介绍如何针对Cortex M0+内核芯片的外设进行开关(使能与失能)设置,控制NXP Keaz128芯片CAN中断开关为例,其他该内核芯片设置方式可进行参考。

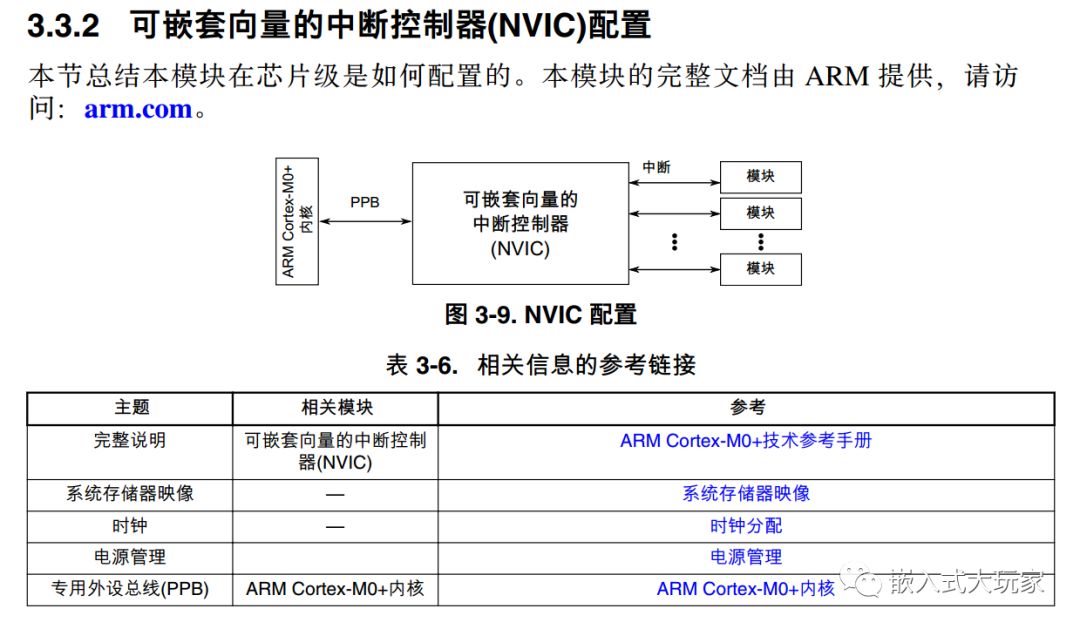

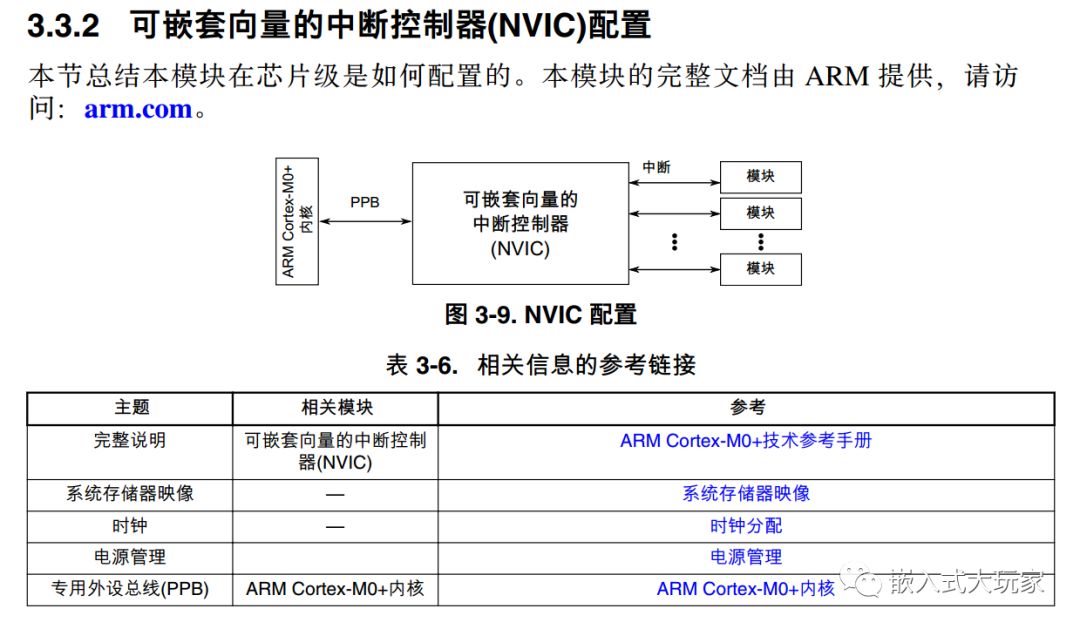

2、NVIC

NVIC:Nested Vectored Interrupt Controller,嵌套向量中断控制器。在ARM内核中由NVIC模块负责中断向量相关设置,自然Cortex M0+内核也不例外。在Keaz128芯片手册关于NVIC一节中内容如下,

其中并没有对NVIC具体寄存器的描述,其属于内核部分内容,故需要查看内核相关文档。在Cortex M0+技术参考手册(Cortex M0+ Technical Reference Manual.pdf)中关于NVIC一章有关于NVIC寄存器的描述如下

由上图可知其寄存器ISER和ICER分别为设置中断使能寄存器和清除中断使能寄存器,具体描述需查看ARMv6-M相关文档,那么查看ARMv6-M体系架构参考手册(ARMv6-M Architecture Reference Manual.pdf)NVIC的部分,其中有上述两个寄存器的具体描述,

由此可知这两个寄存器都为32位,那么只要知道需要设置的外设中断源编号,然后设置这两个寄存器的相应位即可。如keaz128的中断向量分配如下

那么设置NVIC_ISER的30位为1即可实现MSCAN接收中断的使能,其他同理。

3、参考文档

KEA128RM.pdf

Cortex M0+ Technical Reference Manual.pdf

ARMv6-M Architecture Reference Manual.pdf

更多技术内容欢迎关注我的公众号,我们一起讨论

您的关注、转发是对我最大的支持

关注公众号后台留言获取更多资源

其中并没有对NVIC具体寄存器的描述,其属于内核部分内容,故需要查看内核相关文档。在Cortex M0+技术参考手册(Cortex M0+ Technical Reference Manual.pdf)中关于NVIC一章有关于NVIC寄存器的描述如下

其中并没有对NVIC具体寄存器的描述,其属于内核部分内容,故需要查看内核相关文档。在Cortex M0+技术参考手册(Cortex M0+ Technical Reference Manual.pdf)中关于NVIC一章有关于NVIC寄存器的描述如下

由上图可知其寄存器ISER和ICER分别为设置中断使能寄存器和清除中断使能寄存器,具体描述需查看ARMv6-M相关文档,那么查看ARMv6-M体系架构参考手册(ARMv6-M Architecture Reference Manual.pdf)NVIC的部分,其中有上述两个寄存器的具体描述,

由上图可知其寄存器ISER和ICER分别为设置中断使能寄存器和清除中断使能寄存器,具体描述需查看ARMv6-M相关文档,那么查看ARMv6-M体系架构参考手册(ARMv6-M Architecture Reference Manual.pdf)NVIC的部分,其中有上述两个寄存器的具体描述,

由此可知这两个寄存器都为32位,那么只要知道需要设置的外设中断源编号,然后设置这两个寄存器的相应位即可。如keaz128的中断向量分配如下

由此可知这两个寄存器都为32位,那么只要知道需要设置的外设中断源编号,然后设置这两个寄存器的相应位即可。如keaz128的中断向量分配如下

那么设置NVIC_ISER的30位为1即可实现MSCAN接收中断的使能,其他同理。

那么设置NVIC_ISER的30位为1即可实现MSCAN接收中断的使能,其他同理。