class="markdown_views prism-atom-one-light">

数字电子技术实验报告

实验题目:计数器的设计

预习报告

内容一

使用JK触发器设计一个16进制异步减法计数器,并用逻辑分析仪观察并记录CP和每一位的输出波形。

JK触发器功能/真值表

CP时钟 |

J |

K |

工作状态 |

Q+ |

↓

0

0

保持

Q

↓

0

1

置零

0

↓

1

0

置一

1

↓

1

1

翻转

Q

用Proteus设计电路,并运行仿真

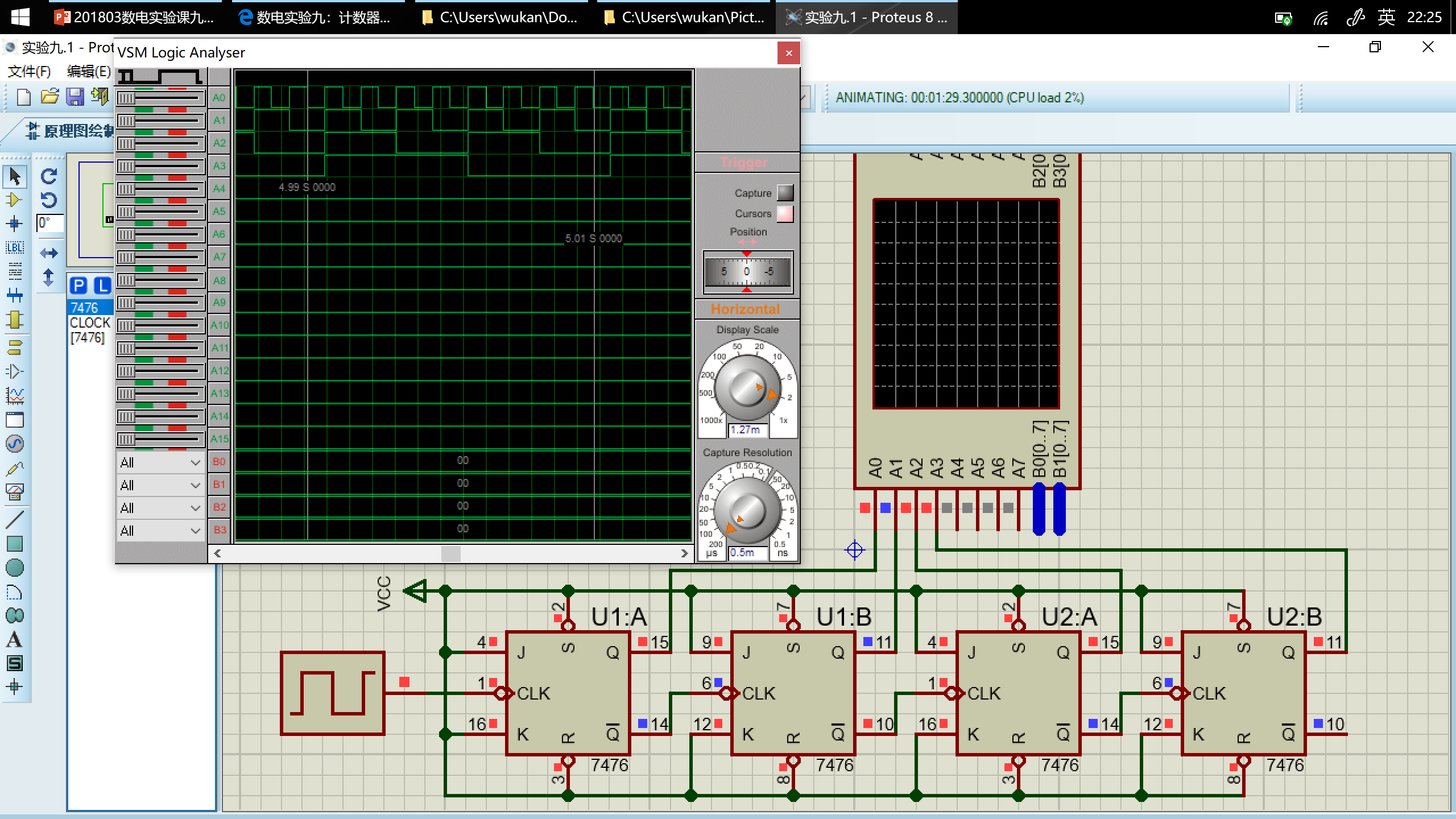

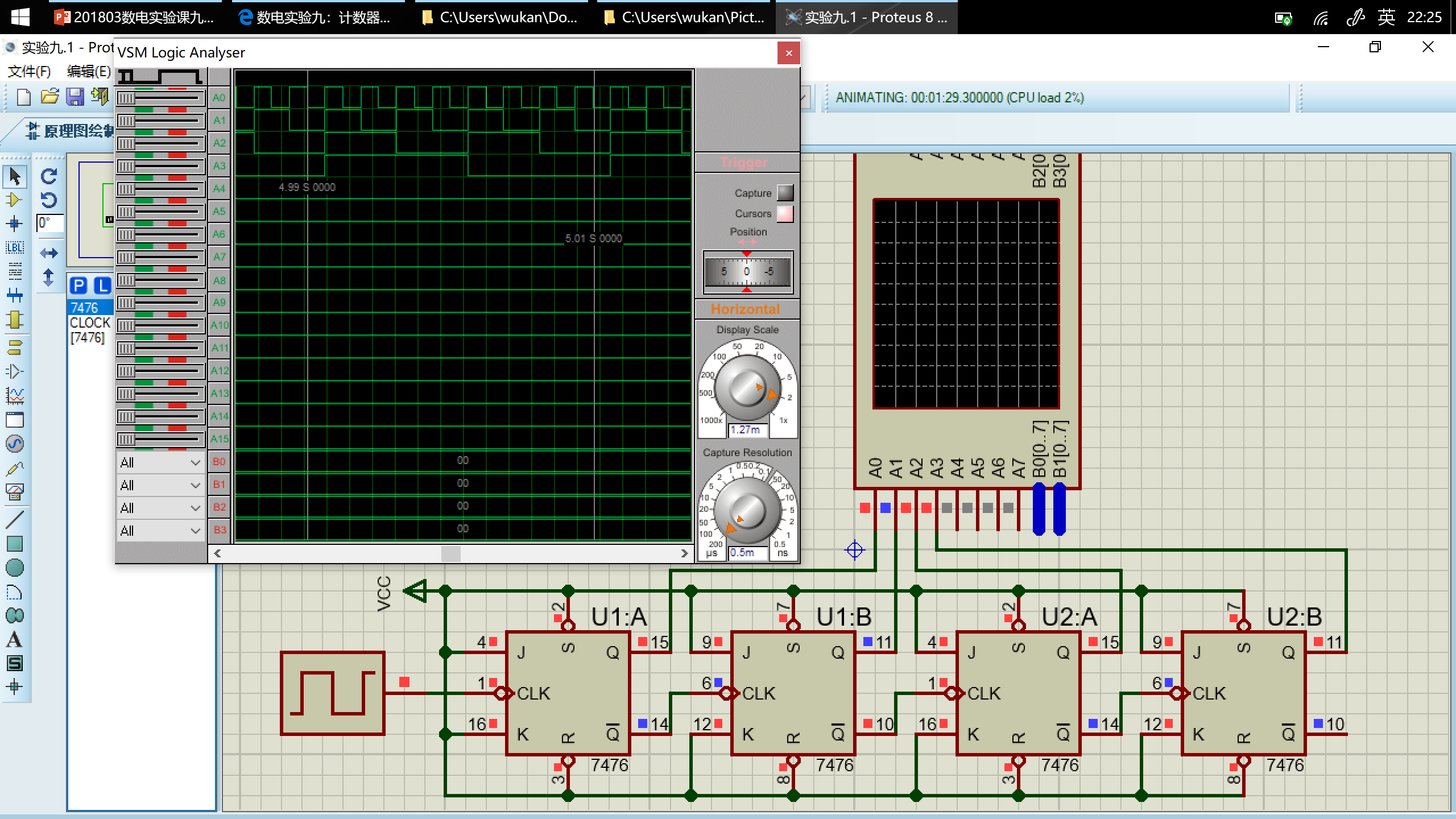

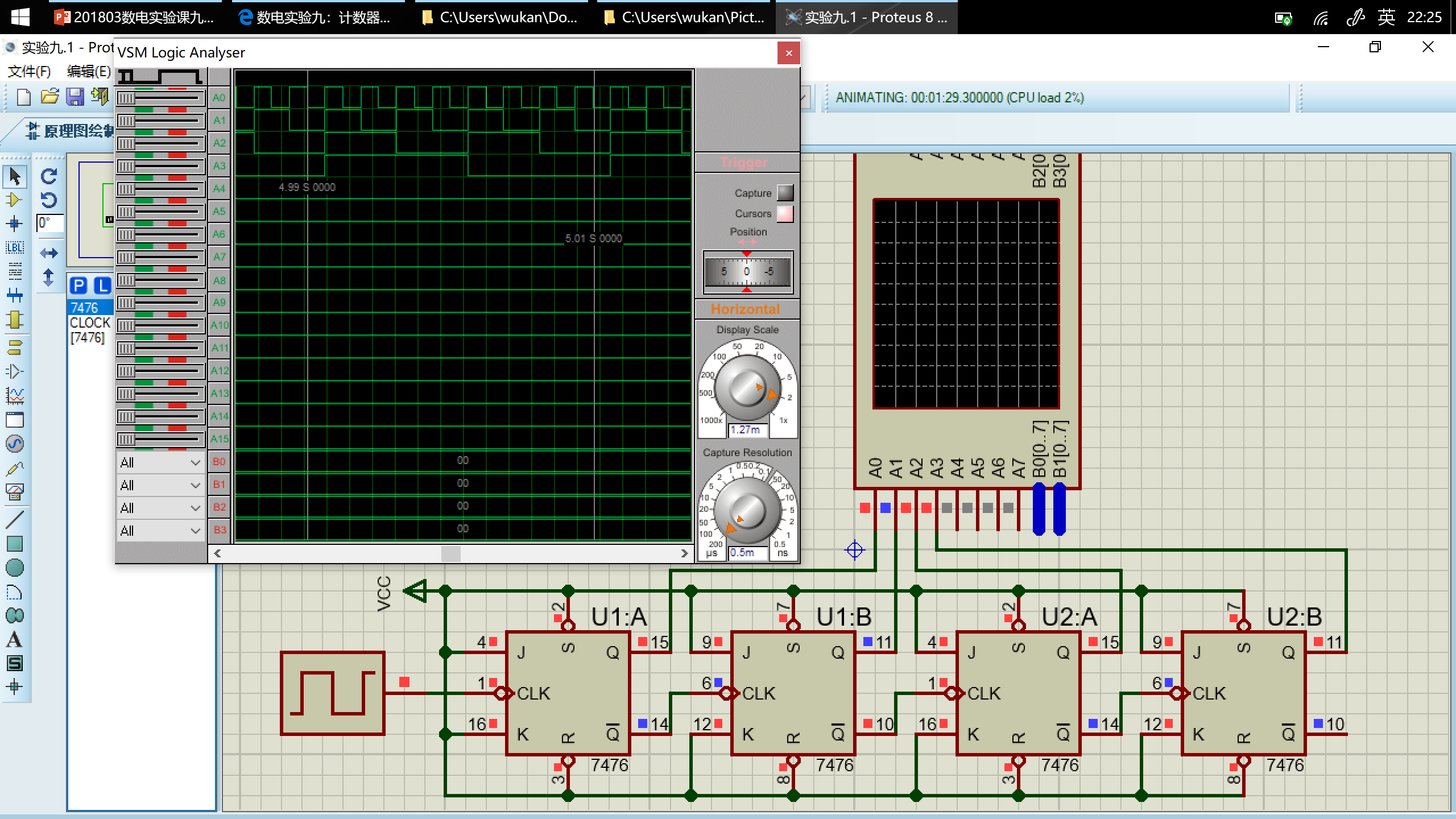

如图,

A0…A3分别对应模拟的

Q0…Q3端口。

可以看出,在一个周期内

Q3Q2Q1Q0的变化顺序依次为

0000→1111→1110→1101→1100→1011→1010→1001→1000→0111→0110→0101→0100→0011→0010→0001→0000→…符合设计预期。

内容二

使用JK触发器设计一个16进制同步加法计数器,并用逻辑分析仪观察并记录CP和每一位的输出波形。

用Proteus设计电路,并运行仿真

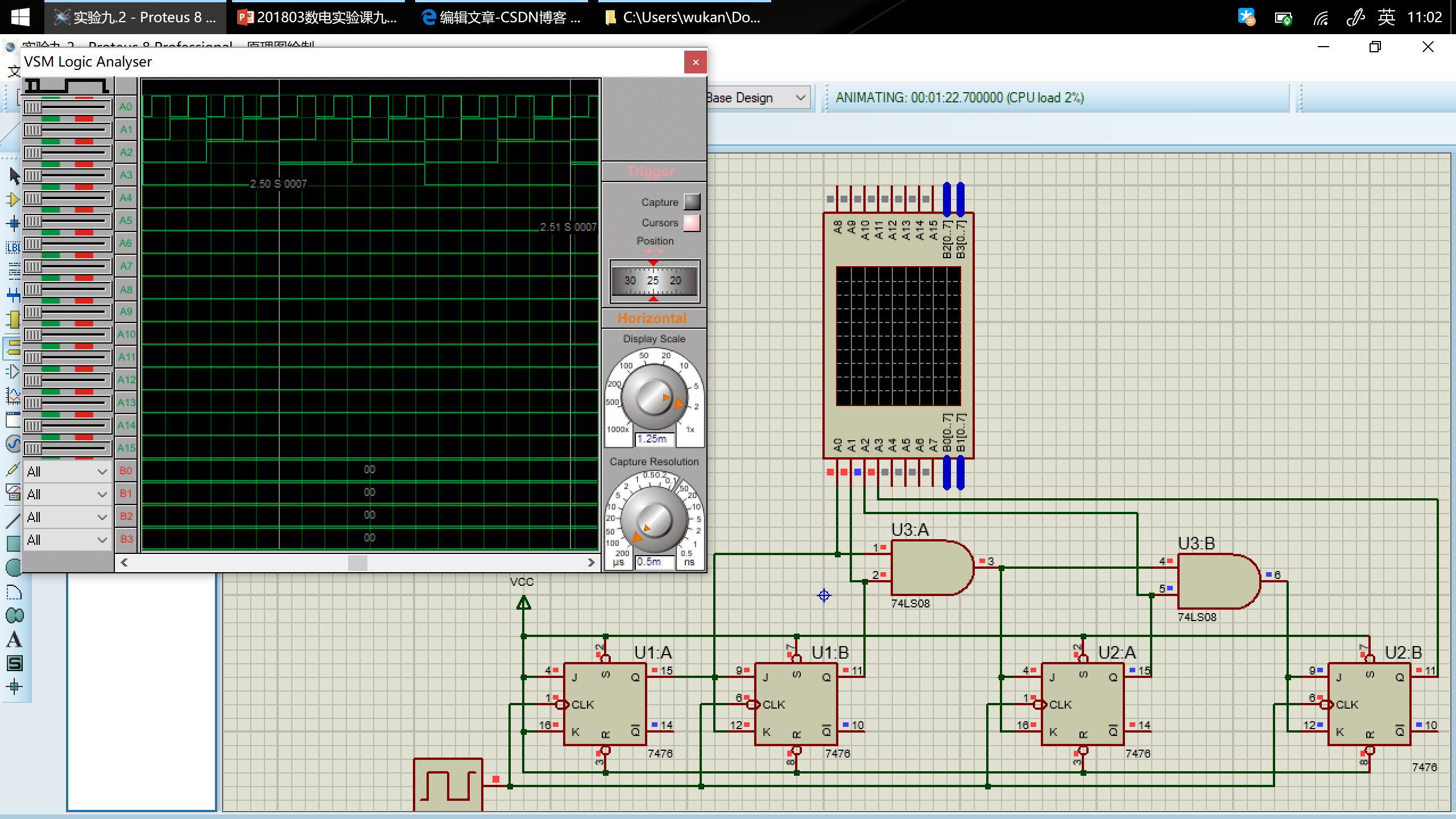

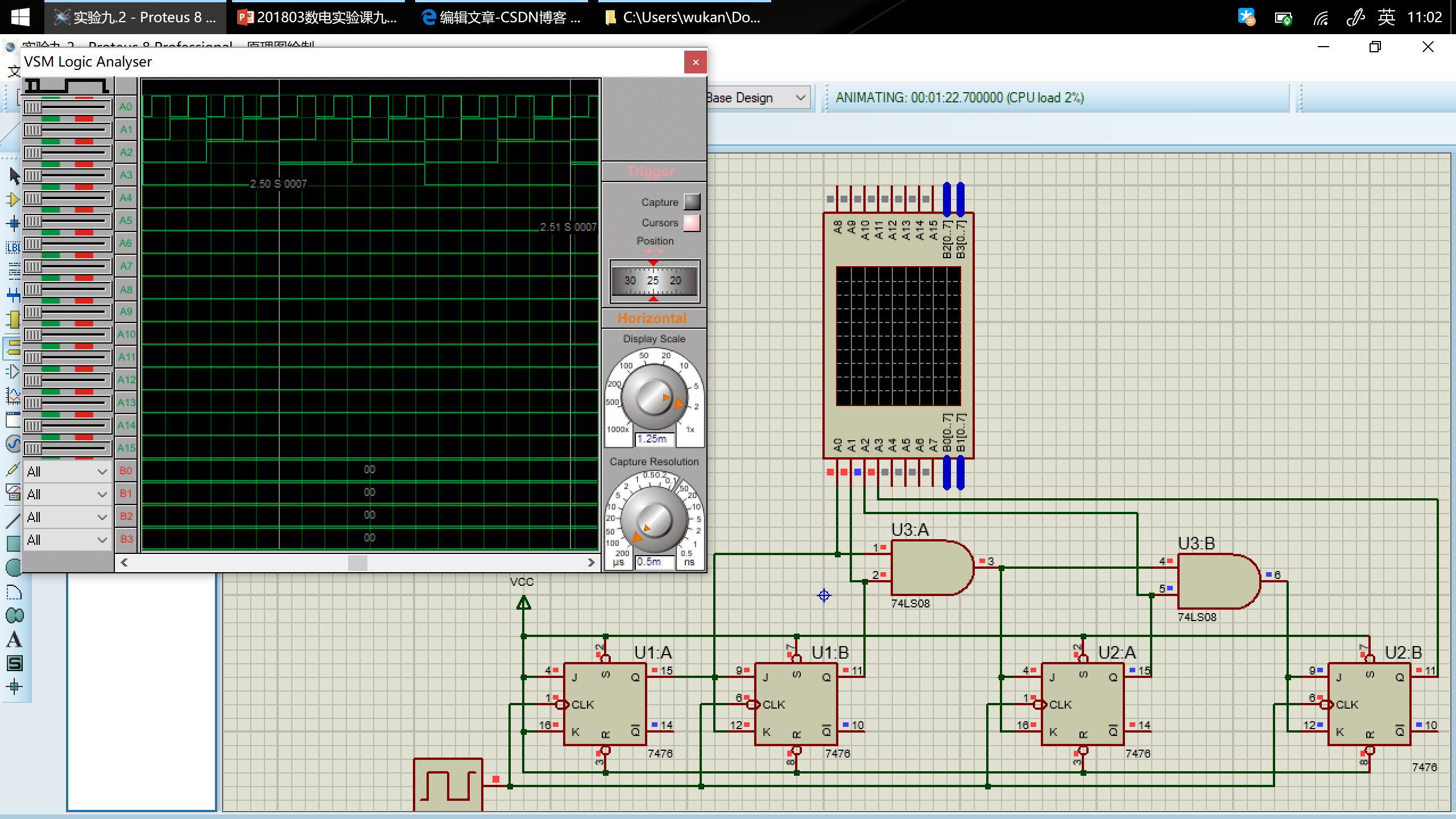

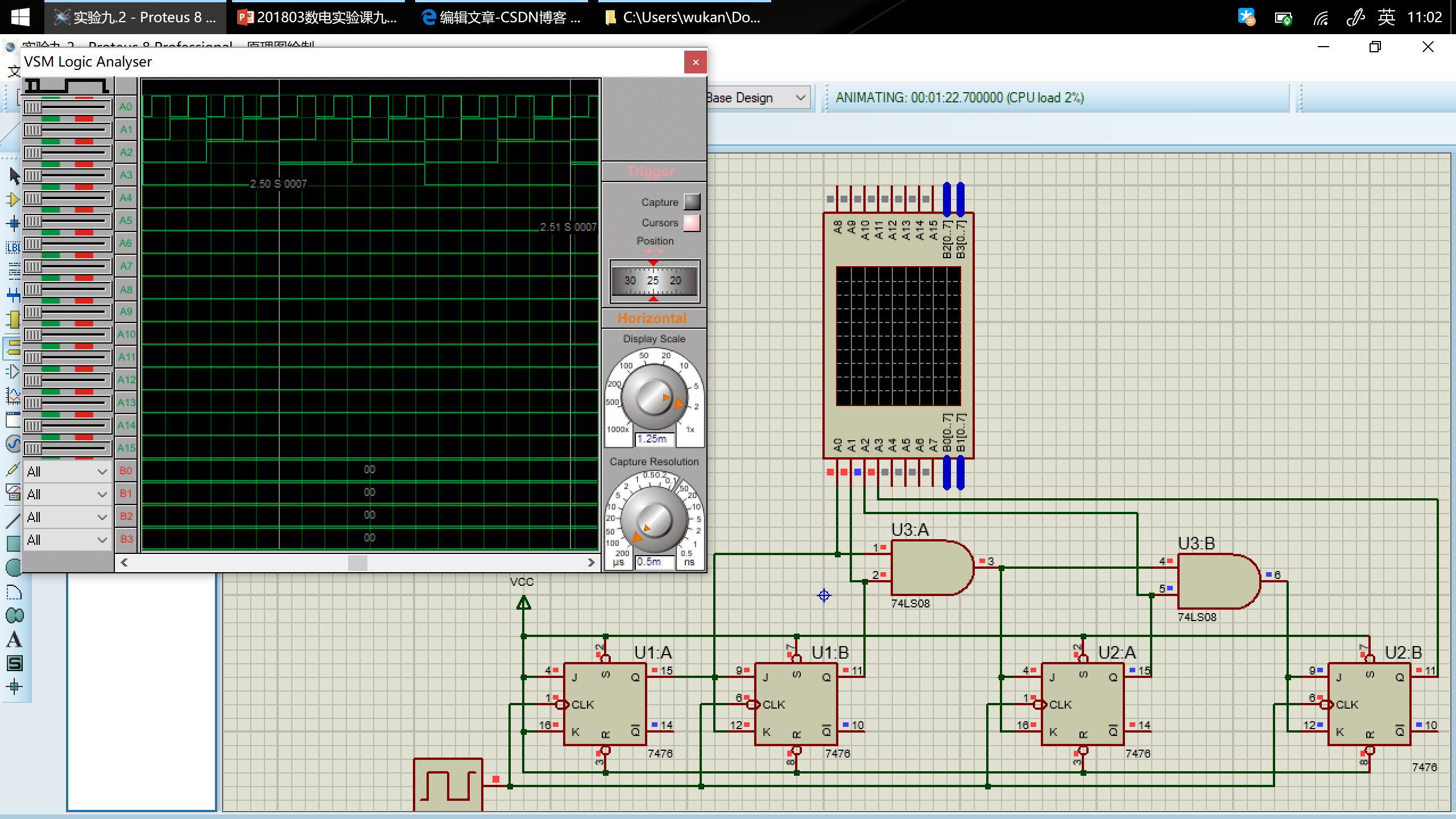

如图,

A0…A3分别对应模拟的

Q0…Q3端口。

可以看出,在一个周期内

Q3Q2Q1Q0的变化顺序依次为

0000→0001→0010→0011→0100→0101→0110→0111→1000→1001→1010→1011→1100→1101→1110→1111→0000…符合设计预期。

内容三

使用JK触发器和门电路设计实现一个二进制四位计数器模仿74LS194功能。要求在实验箱上设计实现左移或右移功能;在proteus软件上实现置零,保持,左移,右移,并行送数功能。

74LS194功能/真值表

CP时钟 |

Cr清零 |

S1 |

S0 |

工作状态 |

QA+ |

QB+ |

QC+ |

QD+ |

↑

0

X

X

置零

0

0

0

0

↑

1

0

0

保持

QA

QB

QC

QD

↑

1

0

1

右移

DSR

QA

QB

QC

↑

1

1

0

左移

QB

QC

QD

DSL

↑

1

1

1

并行送数

D0

D1

D2

D3

用Proteus设计电路,并运行仿真

内容四

用JK触发器和门电路设计一个特殊的12进制同步计数器如下:

0001→0010→0011→0100→0101→0110→0111→1000→1001→1010→1011→1100→0001→…并用逻辑分析仪观察并记录CP和每一位的输出波形。

注意:这个12进制同步计数器没有00状态,要考虑自启动。

次态卡诺图

Q3+Q2+∖Q1+Q

打开微信“扫一扫”,打开网页后点击屏幕右上角分享按钮 |