新手

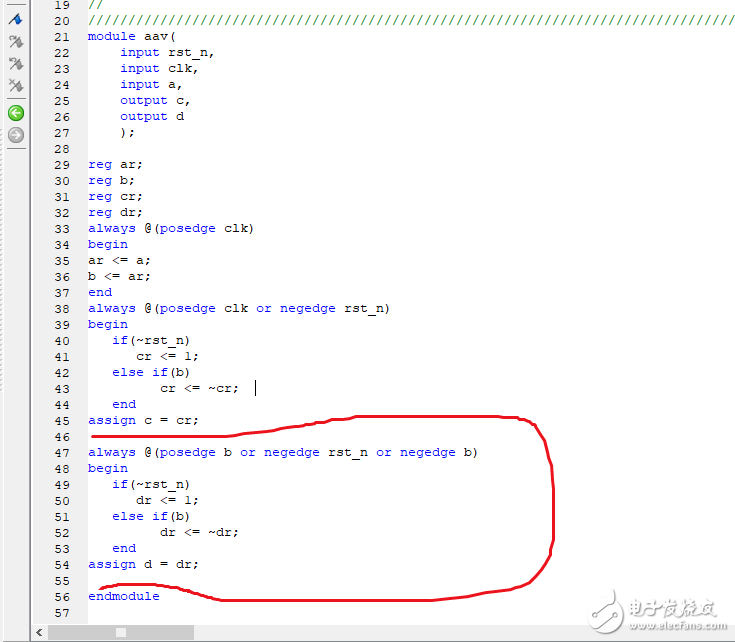

如图是代码和时序图。程序功能 是每个clk上升沿时检测a值(并存入ar,再将ar的存入b),在clk的上升沿同时执行if语句,使每当if(b)为真时,cr翻转,否则不变。

疑问 但我时序仿真时不理解一个地方(即问题1)。

推测 然后我认为是if(b)进行判断的同时,ar在对b进行赋值。由于只有当赋值结束,b才为1,因此,判断时if(b)不为真,维持原输出。

但好像不对,因为dr的输出立刻翻转了。

还是说由always驱动的/reg赋值/和/if语句块/有先后?时钟上升沿时,先if,再赋值?

问题1.我想不明白当b在上升沿时,为什么cr的输出没有立刻翻转,而是延时一个clk周期后翻转?

问题2.另一个dr的输出只是改变了敏感值里的上升沿触发为b的边沿触发,dr的输出就在b上升沿时立刻翻转了,这和cr的区别在哪?

还请各位帮忙解答一下,非常感谢!

-

时序

-

代码

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

clk --------- ---------- ---------- ------------

| | | | | | |

------------ ---------- ---------- ------------

b --------------------------------------------------------------

|

------------------------

cr ---------------------

| |

--------------------------------------------- -------------------

最佳答案

评分

查看全部评分

一周热门 更多>