老师布置的题:

这是我写的代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ppm is

port(

din: in std_logic_vector(7 downto 0);

le: in std_logic;

clk: in std_logic;

rst: in std_logic;

al: out std_logic;

outdata: out std_logic

);

end entity ppm;

architecture ppm1 of ppm is

type st is(idle,s1,s2,s3,s4,s5,s6,s7);

signal state: st;

signal counter0: std_logic_vector(2 downto 0);

signal counter1: std_logic_vector(6 downto 0);

signal dinbuf: std_logic_vector(7 downto 0);

signal regQ: std_logic_vector(1 downto 0);

signal outdatabuf: std_logic;

begin

processcount: process(clk) is

begin

if clk'event and clk='0' then

if state/=idle then

if counter1="1111111" then

counter1<="0000000";

counter0<=counter0+"001";

else

counter1<=counter1+"0000001";

end if;

else

counter1<="0000000";

counter0<="000";

end if;

end if;

end process;

processdinbuf: process(state) is

begin

if state=s1 then

dinbuf<=din;

else

dinbuf<="00000000";

end if;

end process;

processregQ: process(counter0) is

begin

case counter0 is

when "000"=>

regQ(0)<=dinbuf(1);

regQ(1)<=dinbuf(0);

when "001"=>

regQ(0)<=dinbuf(3);

regQ(1)<=dinbuf(2);

when "010"=>

regQ(0)<=dinbuf(5);

regQ(1)<=dinbuf(4);

when "011"=>

regQ(0)<=dinbuf(7);

regQ(1)<=dinbuf(6);

when others=>regQ<="00";

end case;

end process;

processal: process(state) is

begin

case state is

when idle=>al<='0';

when s1|s2|s3|s4|s5|s6=>al<='1';

when others=>al<='0';

end case;

end process;

processst: process(clk) is

begin

if clk'event and clk='1' then

if rst='0' then

dinbuf<="00000000";

counter0<="000";

counter1<="0000000";

regQ<="00";

al<='0';

outdata<='0';

state<=idle;

else

case state is

when idle=>

if le='0' then

state<=idle;

else

state<=s1;

end if;

when s1=>

if counter1<"1111111" then

state<=s1;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s2=>

if counter1<"1111111" then

state<=s2;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s3=>

if counter1<"1111111" then

state<=s3;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=s6;

end case;

end if;

when s4=>

if counter1<"1111111" then

state<=s4;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s5=>

if counter1<"1111111" then

state<=s5;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s6=>

if counter1<"1111111" then

state<=s6;

else

state<=idle;

end if;

when others=>

state<=idle;

end case;

end if;

end if;

end process;

processout: process(state,counter1) is

begin

case state is

when idle=>

outdatabuf<='0';

when s1=>

if counter1<="0001111" then

outdatabuf<='0';

elsif counter1>"0001111" and counter1<="1000111" then

outdatabuf<='1';

elsif counter1>"1000111" and counter1<="1001111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s2=>

if counter1<="0001111" then

outdatabuf<='1';

elsif counter1>"0001111" and counter1<="0011111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s3=>

if counter1<="0100001" then

outdatabuf<='1';

elsif counter1>"0100001" and counter1<="0111111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s4=>

if counter1<="1001111" then

outdatabuf<='1';

elsif counter1>"1001111" and counter1<="1011111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s5=>

if counter1<="1101111" then

outdatabuf<='1';

else

outdatabuf<='0';

end if;

when s6=>

if counter1<="0011111" then

outdatabuf<='1';

elsif counter1>"0011111" and counter1<="0101111" then

outdatabuf<='0';

elsif counter1>"0101111" and counter1<="0111111" then

outdatabuf<='1';

else

outdatabuf<='0';

end if;

when others=>

outdatabuf<='0';

end case;

end process;

outt: process(clk) is

begin

if clk'event and clk='1' then

outdata<=outdatabuf;

end if;

end process;

end architecture ppm1;

这是测试代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ppm_test is

end entity;

architecture ppm_test1 of ppm_test is

component ppm is

port(

din: in std_logic_vector(7 downto 0);

le: in std_logic;

clk: in std_logic;

rst: in std_logic;

al: out std_logic;

outdata: out std_logic

);

end component ppm;

signal clk1: std_logic;

signal din1: std_logic_vector(7 downto 0);

signal rst1: std_logic;

signal le1: std_logic;

signal al1: std_logic;

signal outdata1: std_logic;

begin

ppmm: ppm port map(clk=>clk1,din=>din1,rst=>rst1,le=>le1,al=>al1,outdata=>outdata1);

process

begin

clk1<='0';

wait for 50ns;

clk1<='1';

wait for 50ns;

end process;

process

begin

rst1<='1';

le1<='0';

din1<="00000000";

wait for 180ns;

rst1<='0';

wait for 100ns;

rst1<='1';

wait for 100ns;

le1<='1';

din1<="11100001";

wait for 100ns;

le1<='0';

din1<="00000000";

wait for 10ms;

end process;

end architecture;

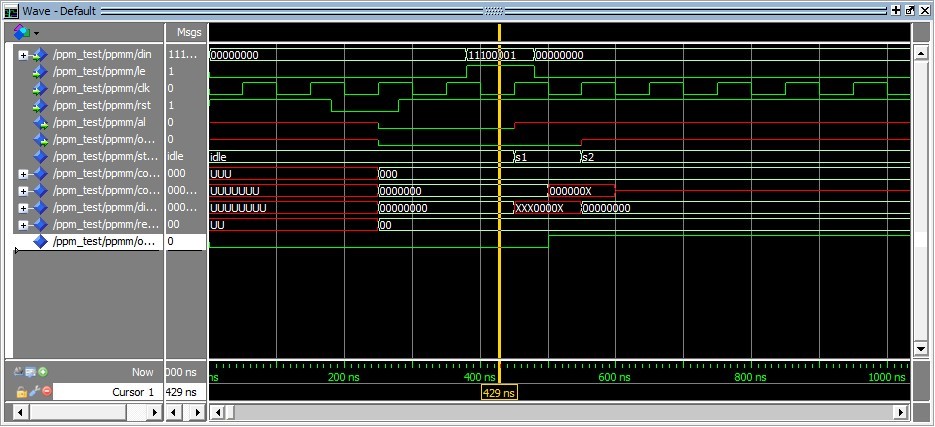

这是仿真图:

我现在特别想知道为什么计数器counter1不工作,还有握手信号al为什么状态机一进s1就立刻变成x;

这是modelsim仿真是说的:# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 650 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 700 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 700 ns Iteration: 1 Instance: /ppm_test/ppmm

求各位大牛帮忙啊,以前没用过vhdl,就上课时学了几天,先谢谢了

这是我写的代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ppm is

port(

din: in std_logic_vector(7 downto 0);

le: in std_logic;

clk: in std_logic;

rst: in std_logic;

al: out std_logic;

outdata: out std_logic

);

end entity ppm;

architecture ppm1 of ppm is

type st is(idle,s1,s2,s3,s4,s5,s6,s7);

signal state: st;

signal counter0: std_logic_vector(2 downto 0);

signal counter1: std_logic_vector(6 downto 0);

signal dinbuf: std_logic_vector(7 downto 0);

signal regQ: std_logic_vector(1 downto 0);

signal outdatabuf: std_logic;

begin

processcount: process(clk) is

begin

if clk'event and clk='0' then

if state/=idle then

if counter1="1111111" then

counter1<="0000000";

counter0<=counter0+"001";

else

counter1<=counter1+"0000001";

end if;

else

counter1<="0000000";

counter0<="000";

end if;

end if;

end process;

processdinbuf: process(state) is

begin

if state=s1 then

dinbuf<=din;

else

dinbuf<="00000000";

end if;

end process;

processregQ: process(counter0) is

begin

case counter0 is

when "000"=>

regQ(0)<=dinbuf(1);

regQ(1)<=dinbuf(0);

when "001"=>

regQ(0)<=dinbuf(3);

regQ(1)<=dinbuf(2);

when "010"=>

regQ(0)<=dinbuf(5);

regQ(1)<=dinbuf(4);

when "011"=>

regQ(0)<=dinbuf(7);

regQ(1)<=dinbuf(6);

when others=>regQ<="00";

end case;

end process;

processal: process(state) is

begin

case state is

when idle=>al<='0';

when s1|s2|s3|s4|s5|s6=>al<='1';

when others=>al<='0';

end case;

end process;

processst: process(clk) is

begin

if clk'event and clk='1' then

if rst='0' then

dinbuf<="00000000";

counter0<="000";

counter1<="0000000";

regQ<="00";

al<='0';

outdata<='0';

state<=idle;

else

case state is

when idle=>

if le='0' then

state<=idle;

else

state<=s1;

end if;

when s1=>

if counter1<"1111111" then

state<=s1;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s2=>

if counter1<"1111111" then

state<=s2;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s3=>

if counter1<"1111111" then

state<=s3;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=s6;

end case;

end if;

when s4=>

if counter1<"1111111" then

state<=s4;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s5=>

if counter1<"1111111" then

state<=s5;

elsif counter0="100" then

state<=s6;

else

case regQ is

when "00"=>state<=s2;

when "01"=>state<=s3;

when "10"=>state<=s4;

when "11"=>state<=s5;

when others=>state<=idle;

end case;

end if;

when s6=>

if counter1<"1111111" then

state<=s6;

else

state<=idle;

end if;

when others=>

state<=idle;

end case;

end if;

end if;

end process;

processout: process(state,counter1) is

begin

case state is

when idle=>

outdatabuf<='0';

when s1=>

if counter1<="0001111" then

outdatabuf<='0';

elsif counter1>"0001111" and counter1<="1000111" then

outdatabuf<='1';

elsif counter1>"1000111" and counter1<="1001111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s2=>

if counter1<="0001111" then

outdatabuf<='1';

elsif counter1>"0001111" and counter1<="0011111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s3=>

if counter1<="0100001" then

outdatabuf<='1';

elsif counter1>"0100001" and counter1<="0111111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s4=>

if counter1<="1001111" then

outdatabuf<='1';

elsif counter1>"1001111" and counter1<="1011111" then

outdatabuf<='0';

else

outdatabuf<='1';

end if;

when s5=>

if counter1<="1101111" then

outdatabuf<='1';

else

outdatabuf<='0';

end if;

when s6=>

if counter1<="0011111" then

outdatabuf<='1';

elsif counter1>"0011111" and counter1<="0101111" then

outdatabuf<='0';

elsif counter1>"0101111" and counter1<="0111111" then

outdatabuf<='1';

else

outdatabuf<='0';

end if;

when others=>

outdatabuf<='0';

end case;

end process;

outt: process(clk) is

begin

if clk'event and clk='1' then

outdata<=outdatabuf;

end if;

end process;

end architecture ppm1;

这是测试代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ppm_test is

end entity;

architecture ppm_test1 of ppm_test is

component ppm is

port(

din: in std_logic_vector(7 downto 0);

le: in std_logic;

clk: in std_logic;

rst: in std_logic;

al: out std_logic;

outdata: out std_logic

);

end component ppm;

signal clk1: std_logic;

signal din1: std_logic_vector(7 downto 0);

signal rst1: std_logic;

signal le1: std_logic;

signal al1: std_logic;

signal outdata1: std_logic;

begin

ppmm: ppm port map(clk=>clk1,din=>din1,rst=>rst1,le=>le1,al=>al1,outdata=>outdata1);

process

begin

clk1<='0';

wait for 50ns;

clk1<='1';

wait for 50ns;

end process;

process

begin

rst1<='1';

le1<='0';

din1<="00000000";

wait for 180ns;

rst1<='0';

wait for 100ns;

rst1<='1';

wait for 100ns;

le1<='1';

din1<="11100001";

wait for 100ns;

le1<='0';

din1<="00000000";

wait for 10ms;

end process;

end architecture;

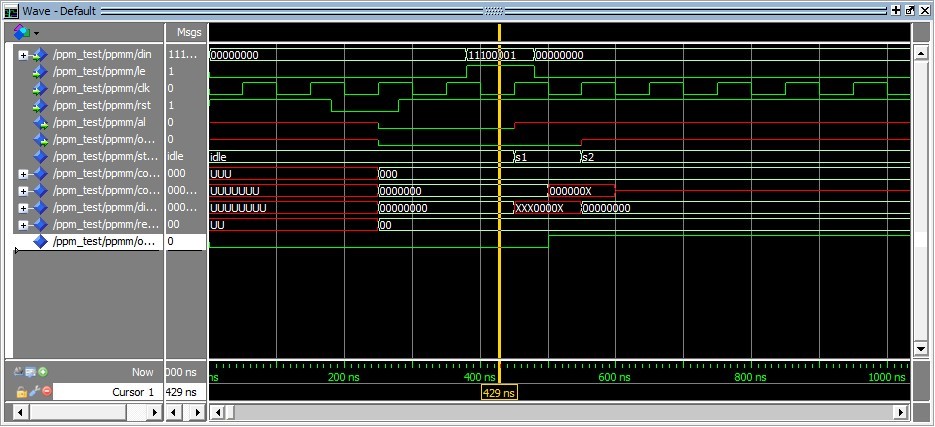

这是仿真图:

我现在特别想知道为什么计数器counter1不工作,还有握手信号al为什么状态机一进s1就立刻变成x;

这是modelsim仿真是说的:# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 500 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 550 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 600 ns Iteration: 2 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 650 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 700 ns Iteration: 1 Instance: /ppm_test/ppmm

# ** Warning: There is an 'U'|'X'|'W'|'Z'|'-' in an arithmetic operand, the result will be 'X'(es).

# Time: 700 ns Iteration: 1 Instance: /ppm_test/ppmm

求各位大牛帮忙啊,以前没用过vhdl,就上课时学了几天,先谢谢了

一周热门 更多>