本帖最后由 ct615 于 2013-11-22 16:55 编辑

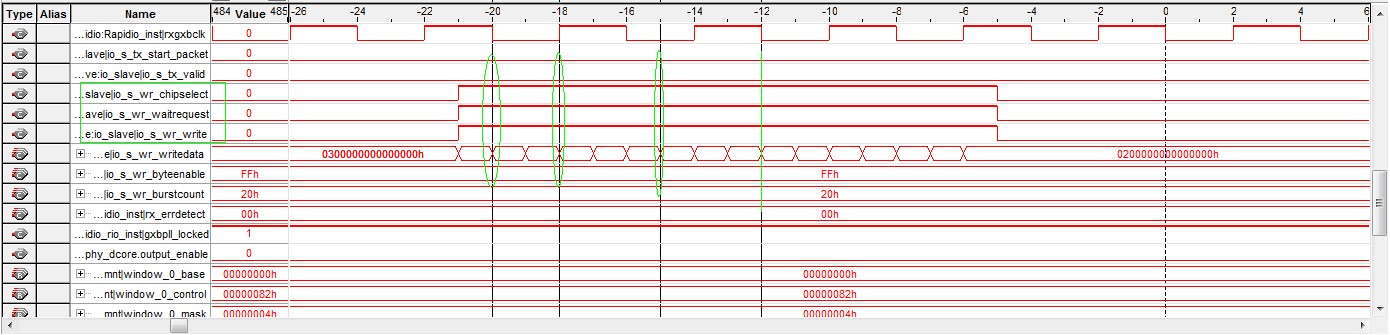

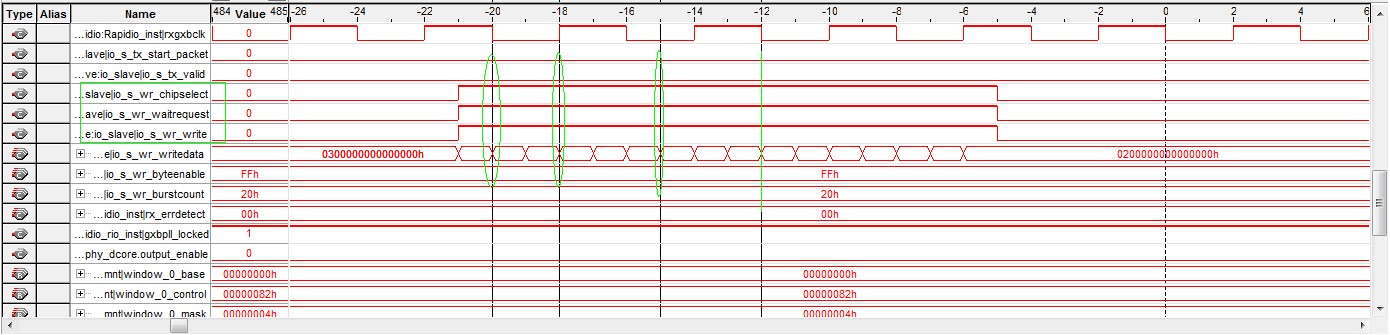

最近在做rapidio 调用altera 的ip core ,FPGA 向外发送数据时,我利用FIFO向Avalon slave interface进行写数据,但是时序上有问题,io_s_wr_waitrequest信号在写使能和片选信号触发的情况下却一直为高电平,数据一直没有写进IO模块,关于这块,有经验的高手指点一下,谢谢

绿 {MOD}区域为时钟上升沿,在上升沿刚好在两个数据的首尾连接处,也就是在时钟的上升沿处没有采集到待写数据

最近在做rapidio 调用altera 的ip core ,FPGA 向外发送数据时,我利用FIFO向Avalon slave interface进行写数据,但是时序上有问题,io_s_wr_waitrequest信号在写使能和片选信号触发的情况下却一直为高电平,数据一直没有写进IO模块,关于这块,有经验的高手指点一下,谢谢

绿 {MOD}区域为时钟上升沿,在上升沿刚好在两个数据的首尾连接处,也就是在时钟的上升沿处没有采集到待写数据

一周热门 更多>