FPGA入门:第一个工程实例之功能仿真概述

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

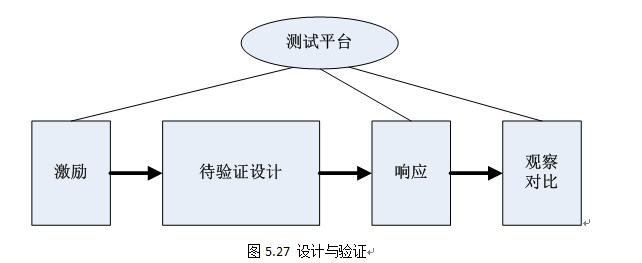

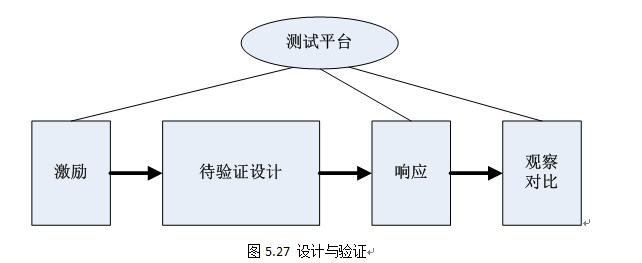

完成了前面基本的设计输入后,为了进一步的验证代码所实现功能的正确性,我们还需要进行仿真测试。关于仿真的一些深入的介绍大家可以参考笔者的《深入浅出玩转FPGA》一书笔记10的相关内容。为了让大家更好的理解什么是仿真、为什么要做仿真以及如何做仿真,这里将以testbench的基本概念进行简单的介绍。当然了,仿真其实在包含在testbench这个大概念里面的。所谓testbench,即测试平台,详细的说就是给待验证的设计添加激励,同时观察它的输出响应是否符合设计要求。如图5.27所示,测试平台就是要模拟一个和待验证设计接口的各种外围设备。

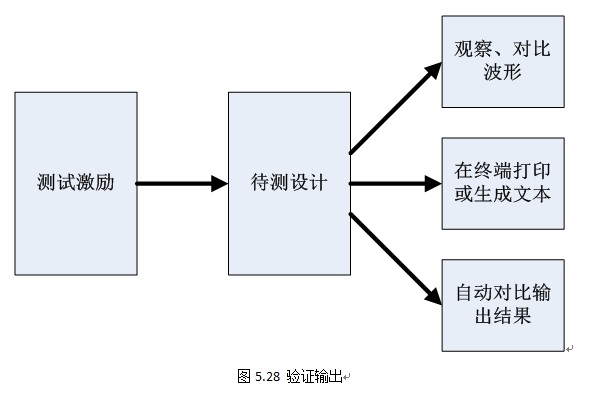

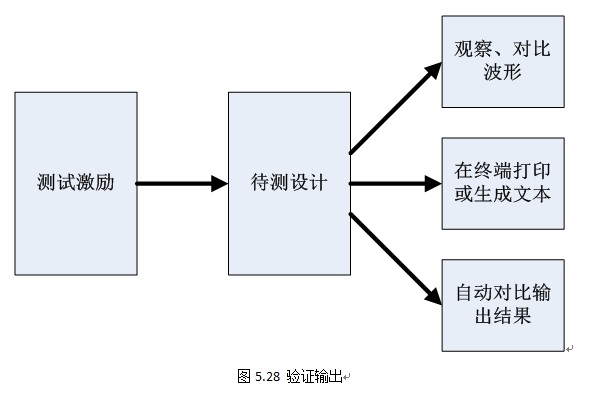

图5.27 设计与验证 仿真测试是FPGA设计流程中必不可少的步骤。在今天的FPGA设计中,如果逻辑规模较大,一般都会使用到IP核或者SOC来加快RTL级设计,所以花费在仿真验证上的工作量往往能够占到这个开发流程的70%。仿真测试的重要性可见一斑。 初学者在刚接触仿真这个概念的时候,可能以为仿真只是简单的用一些开发软件自带的波形发生器产生一些激励,然后观察一下最后的波形输出就完事了。但是对于大规模的设计,用波形产生激励是不现实的,观察波形的工作量也是可想而知的。例如,对于一个16位的输入总线,它可以有65536种组合,如果每次随机产生一种输入,那用波形岂不累死人。再说输出结果的观察,对应65536种输入的65536种输出,看波形肯定让人花眼缭乱。所以,testbench应该有更高效的测试手段。对于FPGA的仿真,使用波形输入产生激励是可以的,观察波形输出以验证测试结果也是可以的,波形也许是最直观的测试手段,但绝不是唯一手段。 如图5.28所示,设计的测试结果判断不仅可以通过观察对比波形,而且可以灵活的使用脚本命令将有用的输出信息打印到终端或者产生文本进行观察,也可以写一段代码让他们自动比较输出结果。总之,testbench的设计是多种多样的,它的语法也是很随意的,不像RTL级设计代码那么多讲究,它是基于行为级的语法,很多高级的语法都可以在脚本中使用。因为它不需要实现到硬件中,它是运行在PC机上的一段脚本,所以相对RTL级可以做得更容易更灵活一些。

图5.28 验证输出 前面我们也以及介绍过Verilog和VHDL都有其相应的行为级的语法,这类语法相对而言更高级一些,它们无需实现到最终的硬件中,而是在PC上运行编译来实现相关功能。而Verilog与VHDL相比,语法更自由一些,或者也可以说更高级一些,它用来写测试脚本更加游刃有余。当然了,业内也出现了一些类似System Verilog、System C等更高级的HDL语言,虽然这些语言出现的初衷都是为了能够最终直接服务于RTL级设计,但实际情况并没有预期的理想,这些语言目前大都只是被用于testbench设计上了。不过对于一般的设计,我们也不用过分追求更高级的语法,行为级的Verilog足够应付大多数的设计验证。

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

完成了前面基本的设计输入后,为了进一步的验证代码所实现功能的正确性,我们还需要进行仿真测试。关于仿真的一些深入的介绍大家可以参考笔者的《深入浅出玩转FPGA》一书笔记10的相关内容。为了让大家更好的理解什么是仿真、为什么要做仿真以及如何做仿真,这里将以testbench的基本概念进行简单的介绍。当然了,仿真其实在包含在testbench这个大概念里面的。所谓testbench,即测试平台,详细的说就是给待验证的设计添加激励,同时观察它的输出响应是否符合设计要求。如图5.27所示,测试平台就是要模拟一个和待验证设计接口的各种外围设备。

图5.27 设计与验证 仿真测试是FPGA设计流程中必不可少的步骤。在今天的FPGA设计中,如果逻辑规模较大,一般都会使用到IP核或者SOC来加快RTL级设计,所以花费在仿真验证上的工作量往往能够占到这个开发流程的70%。仿真测试的重要性可见一斑。 初学者在刚接触仿真这个概念的时候,可能以为仿真只是简单的用一些开发软件自带的波形发生器产生一些激励,然后观察一下最后的波形输出就完事了。但是对于大规模的设计,用波形产生激励是不现实的,观察波形的工作量也是可想而知的。例如,对于一个16位的输入总线,它可以有65536种组合,如果每次随机产生一种输入,那用波形岂不累死人。再说输出结果的观察,对应65536种输入的65536种输出,看波形肯定让人花眼缭乱。所以,testbench应该有更高效的测试手段。对于FPGA的仿真,使用波形输入产生激励是可以的,观察波形输出以验证测试结果也是可以的,波形也许是最直观的测试手段,但绝不是唯一手段。 如图5.28所示,设计的测试结果判断不仅可以通过观察对比波形,而且可以灵活的使用脚本命令将有用的输出信息打印到终端或者产生文本进行观察,也可以写一段代码让他们自动比较输出结果。总之,testbench的设计是多种多样的,它的语法也是很随意的,不像RTL级设计代码那么多讲究,它是基于行为级的语法,很多高级的语法都可以在脚本中使用。因为它不需要实现到硬件中,它是运行在PC机上的一段脚本,所以相对RTL级可以做得更容易更灵活一些。

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

一周热门 更多>