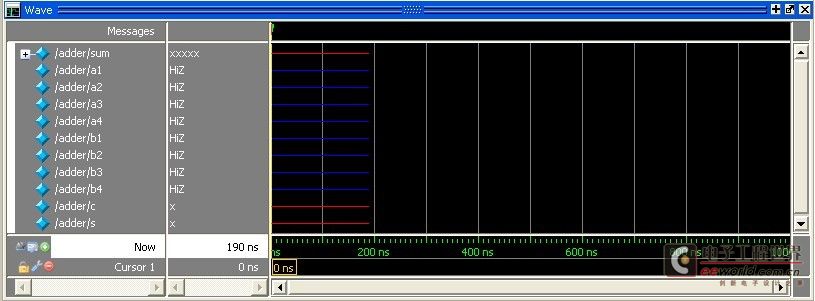

编了一个verilog的四位无符号加法器、测试信号的仿真没有问题了、但是主程序的仿真仿不出来、不知道是调用的问题还是别的,请大家帮忙查错

测试信号:

[ 本帖最后由 fengyiyong 于 2012-12-6 22:49 编辑 ] 此帖出自小平头技术问答

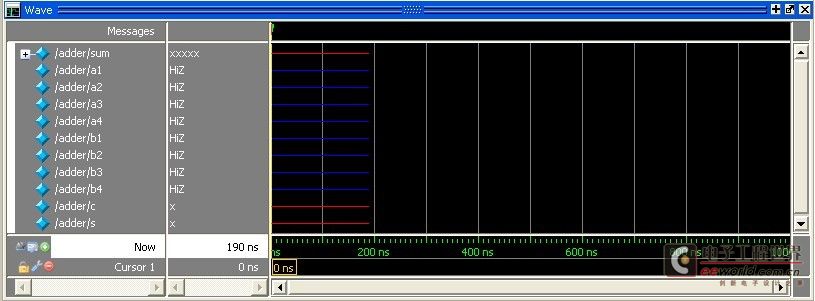

测试信号:

- `include "adder.v"

- module adder_tb();

- reg[3:0]addend,adder;//加数和被加数

- reg a1,a2,a3,a4,b1,b2,b3,b4,c0;//各个位和初始进位

- initial

- begin

- addend=4'b0001;//被加数为1

- adder=4'b0010;//加数为2

- c0=1'b0;

- a1=addend[0];

- a2=addend[1];

- a3=addend[2];

- a4=addend[3];

- b1=adder[0];

- b2=adder[1];

- b3=adder[2];

- b4=adder[3];

- end

- adder m(.a1(a1),.a2(a2),.a3(a3),.a4(a4),.b1(b1),.b2(b2),.b3(b3),.b4(b4),.c0(c0));//调用

- endmodule

- module adder(a1,a2,a3,a4,b1,b2,b3,b4,c0,sum);

- input a1,a2,a3,a4,b1,b2,b3,b4,c0;

- output[4:0] sum;

- reg[4:0] sum;

- wire c1,c2,c3,c4;//中间进位

- always@(*)

- sum[0]=((~a1)&(~b1)&c0)|((~a1)&b1&(~c0))|(a1&(~b1)&(~c0))|(a1&b1&c0);

- always@(*)

- sum[1]=((~a2)&(~b2)&c1)|((~a2)&b2&(~c1))|(a2&(~b2)&(~c1))|(a2&b2&c1);

- always@(*)

- sum[2]=((~a3)&(~b3)&c2)|((~a3)&b3&(~c2))|(a3&(~b3)&(~c2))|(a3&b3&c2);

- always@(*)

- begin

- sum[3]=((~a4)&(~b4)&c3)|((~a4)&b4&(~c3))|(a4&(~b4)&(~c3))|(a4&b4&c3);

- sum[4]=c4;

- end

- assign c1=(a1&b1)|(a1&(~b1)&c0)|((~a1)&b1&c0);

- assign c2=(a2&b2)|(a2&(~b2)&c1)|((~a2)&b2&c1);

- assign c3=(a3&b3)|(a3&(~b3)&c2)|((~a3)&b3&c2);

- assign c4=(a4&b4)|(a4&(~b4)&c3)|((~a4)&b4&c3);

- endmodule

[ 本帖最后由 fengyiyong 于 2012-12-6 22:49 编辑 ] 此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

你可以在TB文件中,过上10个时间单位(#10),将加数和被加数改动一次,这样就可以触发主程序了。

一周热门 更多>