小弟近日使用了一块L3G4200陀螺仪与FPGA进行通信,使用的是SPI总线,并参考Altera的应用笔记《SPI CORE》和《Nios》,现在使用Altera提供的HAL APIalt_avalon_spi_command()函数与陀螺仪通讯。

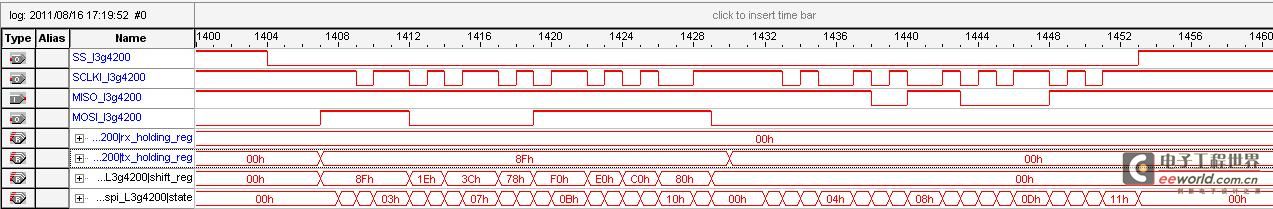

使用Signal Tap逻辑分析仪读取数据如下:

如图所示,MOSI为FPGA输出,外设输入端;MISO为FPGA输入,外设输出端。图中MOSI数据为向陀螺仪发出的读取"WHO_AM_I"寄存器的指令,MISO数据为陀螺仪想FPGA的应答。

图中tx_holding_reg/rx_holding_reg为IP核中定义的数据发送/接收寄存器shift_reg为移位用寄存器(只有一个,可能是发送和接收共用)

现在发现如下问题:外设已经对FPGA应答,且FPGA管脚(MISO)上已经接受到电平变化,为什么没有写进rx寄存器?

另:运行在Nios上的函数无法接受到数据,函数本质是一个读寄存器程序。

求解答,大恩不言谢 此帖出自小平头技术问答

此帖出自小平头技术问答

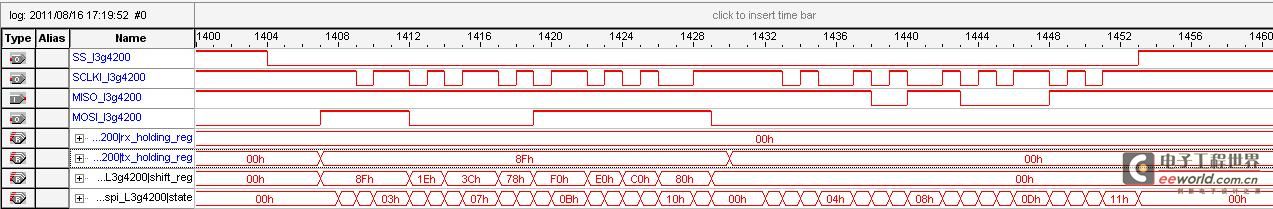

使用Signal Tap逻辑分析仪读取数据如下:

如图所示,MOSI为FPGA输出,外设输入端;MISO为FPGA输入,外设输出端。图中MOSI数据为向陀螺仪发出的读取"WHO_AM_I"寄存器的指令,MISO数据为陀螺仪想FPGA的应答。

图中tx_holding_reg/rx_holding_reg为IP核中定义的数据发送/接收寄存器shift_reg为移位用寄存器(只有一个,可能是发送和接收共用)

现在发现如下问题:外设已经对FPGA应答,且FPGA管脚(MISO)上已经接受到电平变化,为什么没有写进rx寄存器?

另:运行在Nios上的函数无法接受到数据,函数本质是一个读寄存器程序。

求解答,大恩不言谢

此帖出自小平头技术问答

此帖出自小平头技术问答

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

找到原因了,外设默认输出高点平,估计是Nios不能识别低电平中断,加一个非门就好了。

一周热门 更多>